机器之心转载

原作者:包云岗

近日,五位来自中国科学院大学的2016级本科生,带着自己设计的处理器芯片「果壳」正式毕业,这一成果引发媒体热议,被网友称为「最硬核毕业证」。作为「一生一芯」计划的负责人,中科院计算所研究员包云岗也在社交平台上阐述了本次探索与实践背后的故事。

据中国青年报消息,近日,中国科学院大学(以下简称国科大)2016级计算机学院金越、王华强、王凯帆、张林隽和张紫飞五位本科生,主导完成了一款64位RISC-V处理器SoC芯片设计并成功流片,实现在芯片上成功运行Linux操作系统以及学生自己编写的国科大教学操作系统UCAS-Core。

这是国科大「一生一芯」计划的首期成果,也是五位本科生珍贵的毕业纪念品,被网友称为「最硬核毕业证」,在社交媒体平台上引发热议。

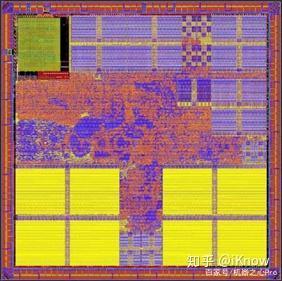

7月25日,国科大在玉泉路校区礼堂报告厅举行新闻发布会,详细介绍了这一成果。据了解,上述64位RISC-V处理器名为「果壳(NutShell)」,基于中芯国际110nm工艺。目前,「果壳」团队的投稿已被RISC-V全球论坛接收,团队将在9月3日向全球业界介绍「果壳」的设计。「果壳」设计代码也已正式开源。

项目地址:

国科大计算机科学与技术学院院长、中科院计算所所长孙凝晖院士表示:「处理器芯片被公认为芯片产业皇冠上的明珠,设计复杂度高、难度大。我国处理器芯片设计人才严重紧缺,如何加快此类人才的培养规模与培养速度,是我国迫在眉睫的难题。」

2019年5月,美国政府以「科技网络安全」为由,将华为及其70个分支机构列入「实体清单」,禁止华为在未经美国政府批准的情况下从美国企业获得元器件和相关技术。五个月后,美国商务部产业安全局(BIS)又将28家中国实体加入「实体清单」,包括海康威视、大华股份、科大讯飞、旷视科技、商汤科技、美亚柏科等多家科技企业。

在步步紧逼的态势下,我们必须承认,中国需要中长期的先进技术,更需要的是处理器芯片设计人才。

针对处理器设计人才危机,国科大于2019年8月启动了「一生一芯」计划,目标是通过让本科生设计处理器芯片并完成流片,培养具有扎实理论与实践经验的处理器芯片设计人才。

去年,国科大在本科新生录取通知书中嵌入了「龙芯三号」芯片,被网友称为「硬核录取通知书」,让人记忆犹新。这一次,硬核毕业证「果壳」诞生的背后,又有着怎样的探索与挑战?

包云岗:「一生一芯」背后的故事

中国科学院计算技术研究所研究员包云岗也是「一生一芯」计划的负责人,他在知乎上详细介绍了该计划的启动与实施历程。

原文内容整理如下:

一、酝酿

2018年11月8日,乌镇,世界互联网大会,经过9个月筹备工作,中国开发指令生态(RISC-V)联盟正式成立。晚上在乌镇的一家餐馆庆祝时,坐在我边上的一位老师问了个问题:「以后打算怎么做开源芯片生态?」其实这也是在2018年期间我经常问自己的一个问题,我有一个很粗的想法——能不能让学生参与到开源芯片生态建设中——经常会浮现出来。听了那位老师的问题,我在脑海中又浮现出这个想法,然后就在饭桌上一边整理思路一边介绍如何将教学和开源芯片结合起来。这应该是「一生一芯」计划的最初萌芽。

那时还没想到「一生一芯」这个名字,但已经大致形成了这样的目标——让本科生也能做处理器芯片,让本科生能带着自己设计的处理器芯片毕业。但联盟成立后,这个想法并没有实质性推动。

2019年5月16日华为被美国列入实体名单,全国震惊。各界都在想能为华为做些什么,我们也在思考。但是,我们是做开源芯片的,华为暂时还用不上;我们采用的是开放的RISC-V指令集,而华为的主力芯片都是基于ARM。看起来我们是无法帮助华为解决燃眉之急了。但和华为专家交流后,他们说短期内的需求华为自己基本能应对,他们更需要的是中长期的先进技术,而最需要的是处理器芯片设计人才。因为华为的芯片架构设计团队很多在美国硅谷,由于美国的出口管制,虽然是华为的全资子公司,但其技术也不能输入到华为总部。这导致华为在美国的芯片设计人才不能再发挥作用,但在国内又招不到这样的人才。这才是华为的心腹之患。

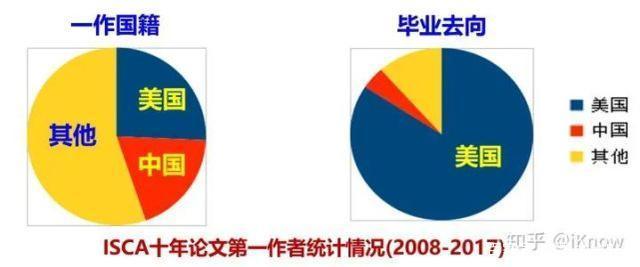

华为在国内找不到处理器芯片设计人才的情况是在意料之中。2017年,我曾安排组里的学生统计过2008~2017十年的体系结构顶级会议ISCA论文第一作者的情况,最后统计数据发现这些优秀人才85%选择在美国就业,仅有4%在中国就业,差距巨大。这和国内很多大学不开展处理器芯片设计相关教学与研究密切相关。

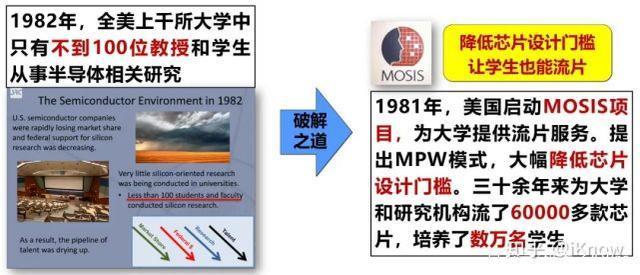

事实上,类似的人才危机美国也曾经历过,1982年全美上千所大学中只有不到100位教授和学生从事半导体相关的研究。为了应对人才危机,美国国防部高级研究计划署(DARPA)在1981年启动MOSIS项目,为大学提供流片服务,通过MPW模式大幅降低芯片设计门槛。30余年来MOSIS为大学和研究机构流了多款芯片,培养了数万名学生。

由此可见,降低芯片设计门槛,让学生能设计自己的芯片并流片,可大幅提高人才培养效率。这和我此前的构想和目标完全一致。我们不能再耽误了,要加速人才培养计划。

二、正式启动

我自作主张地给这个计划起了个名字:「一生一芯」。初衷是希望有一天能让每一个学生都能带着自己设计的芯片毕业,不管未来是不是真得能实现,这至少听起来是一个美好的理想,而且还有一点烂漫——后来很多人听到这个名字,第一印象大多是「一辈子做一颗芯片」。还有女生有更浪漫地理解:「一生一心一意爱一人」。不管如何,看来大家对这个名字似乎还都不反感。

然后,我又联系了几位国科大本科生,询问他们愿不愿意参加这个「一生一芯」计划当小白鼠。出于意料地是,这些准00后(98/99出生)都表示愿意挑战一下,愿意当小白鼠。

6月20日,我在开源芯片工作组群向大家宣布:启动「一生一芯」计划!这并不是研制产品级芯片,而是一次教学实践。很快唐丹老师为未来的芯片起好了内部代号「COOSCA」,三门课ComputerOrganization/OperatingSystem/ComputerArchitecture的缩写。

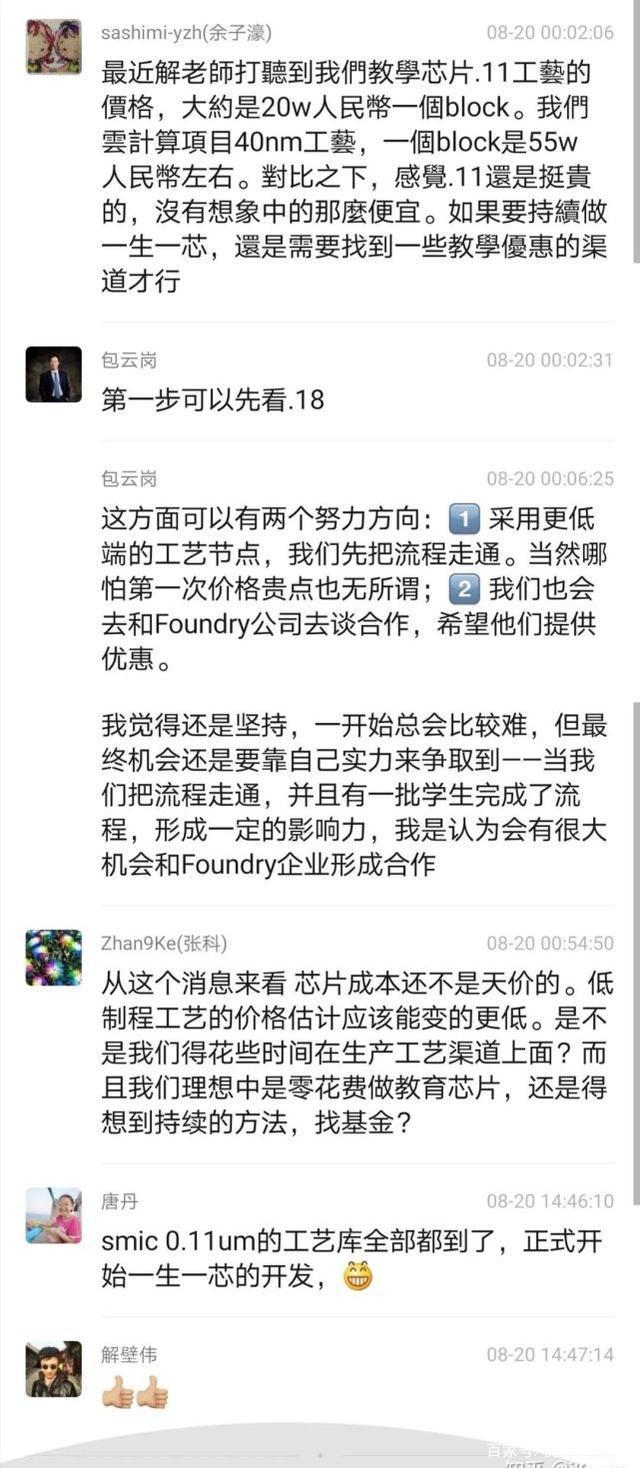

随后开始组建教学团队,随着项目的进行教学团队也在不断扩大:唐丹老师和工程师刘彤负责SoC架构设计指导,余子濠老师负责处理器核设计(其实子濠还是博士生,但因为在国内计算机系统教学领域很有名,所以我们也半开玩笑地叫他老师),张科老师负责项目协调、与国科大对接,并和常轶松老师、赵然老师一起在FPGA模拟仿真方面进行指导,解壁伟老师和李峄工程师在后端物理设计上给予支持,深圳大学蔡晔老师则参与帮助设计PCB板卡,另外蒋德钧老师和王卅老师是国科大本科操作系统任课老师,在操作系统方面给予支持,两位博士生王诲喆与徐易难也担任起助教的角色,帮助答疑解惑。而我自己,则更像是一个啦啦队长,给大家打鸡血。

教学团队开始行动起来了,大家讨论制定总体方案,确定技术路线,选择基础平台,搭建开发环境,选择流片工艺和班车……参加首期「一生一芯」计划的同学也最终确定,一共有五位,他们是金越、王华强、王凯帆、张林隽和张紫飞。这五位同学通过了计算所暑期夏令营面试,均被录取为计算所研究生,其中金越导师是陈明宇研究员,王华强导师是蒋德钧副研究员,王凯帆导师是孙凝晖院士,张林隽和张紫飞的导师则是我。但接下来的时间,他们将组成一个团队,一起挑战带着自己设计的处理器芯片毕业这个任务。

8月20日,当唐丹老师和解壁伟老师终于落实中芯国际110nm工艺的流片渠道后,「一生一芯」计划一切准备就绪。

8月27日,参加「一生一芯」计划的首批五位同学和教学团队一起在我的办公室开了一次简单但意义重大的动员大会。「一生一芯」计划正式启动!

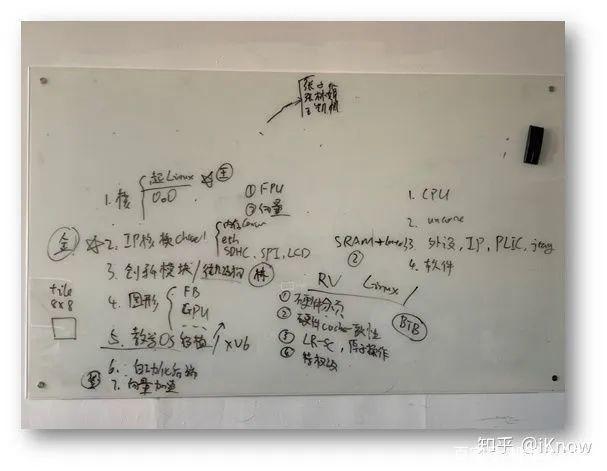

项目分工

三、四个月高强度开发

开弓没有回头箭。唐丹老师确定了最合适的流片班车是12月17日,距离动员大会不到4个月!这样芯片能在4月份完成封装,返回进行测试。如果一切顺利,那就可以赶上五月底或六月初的国科大本科毕业答辩,到时可以在答辩现场展示芯片。但是如果错过这趟班车,那就需要再等2个月赶下一趟班车,这就意味着芯片不可能在毕业答辩时返回。「一生一芯」团队需要跟时间赛跑。

我们在确定总体方案时有两个决定:

一是用Chisel开发,此前我们实验室做过Chisel与Verilog在开发效率和开发质量上的对比实验,证明Chisel能数倍替身开发速度,同时开发质量不比Verilog差,相关结果发表在论文《芯片敏捷开发实践:标签化RISC-V》。

二是以余子濠为南大开发的一款教学RISC-V处理器核为基础进行改进,这主要是因为余子濠在开发这款处理器的过程中构建了丰富的工具,包括NEMU软件模拟器、指令差分测试框架等,这些都有助于加速开发。而教学处理器功能还很基础,要能运行Linux并且支持流片,需要新增大量新功能,包括RV64IM/RVC/RVA等指令扩展、时钟中断、硬件填充的TLB、M/S/U特权级、缺页异常、Cache预取、SDRAM控制器、外围I/O设备……这是一种贴近实战的开发模式——实际的产品研发和科研工作中,往往不是总是从头开始,更多的是在已有的基础上,增加新的功能,提高性能等等。这就需要培养学生「理解-消化-创新」的能力。

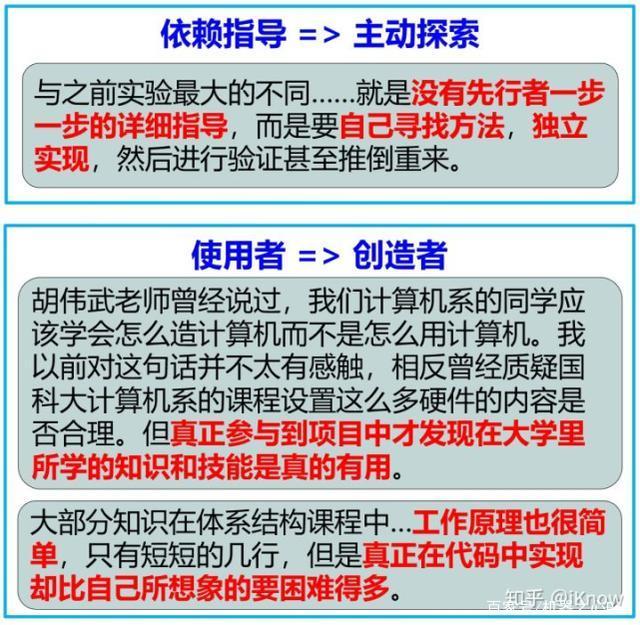

接下来是4个月高强度的开发,然而有些关键模块的工作原理是课堂上没有介绍过的,同学们还需要进行一些探索性的尝试,有时甚至需要将此前的设计推倒重来,他们会因此感到焦虑或沮丧,这对他们的心态也是很大的考验。教学团队不仅仅需要给予技术指导,还需要对学生的心态进行正确的引导,告诉他们不确定性是探索过程中的客观规律,然后引导他们去总结探索失败的经验,去深刻地分析当前方案不可行的原因,从而加深对问题的理解,让他们正确认识到探索失败的意义。

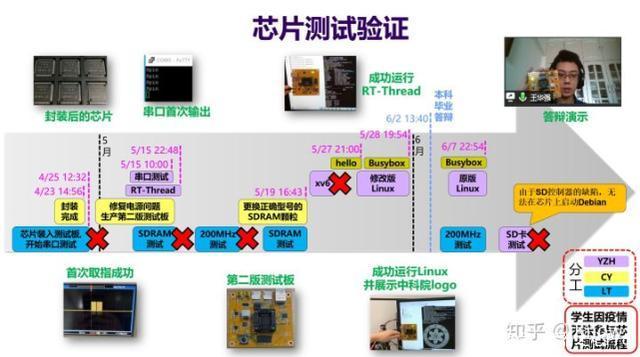

虽然任务极具挑战,但不断有进展。每取得一个小里程碑,大家都会记录下那个时刻,精确到分钟,因为觉得未来有一天也许用得上。后来,这些时刻真的用上了,就是宣传视频中的那条时间线。这个过程中,国科大各方给了很大的支持,从校领导到本科部、计算机学院各级都很关心和重视;在中科院计算所,所长孙凝晖院士、主管教学的陈熙霖副所长、教育处李琳老师等都给予全方位的保障与支持。这也赋予了「一生一芯」团队某种使命感,更激发了大家的斗志。

12月19日,COOSCA1.0芯片版图冻结。当唐丹老师告知版图已经正式提交,大家就如高考交卷,终于舒了一口气,却又悬起了一颗心。

四、疫情中的测试验证

等待芯片返回是一种既期盼又担忧的感觉。这种感觉又进一步被突如其来的疫情放大了。当1月23日宣布武汉封城后疫情不断发展,我们也越来越担忧正在流片中的那颗COOSCA芯片还能不能按时回来,还能不能赶上毕业答辩。出乎意外的是芯片基本按照预期时间返回了,在这里我们要对中芯国际和封测企业的员工们表达深深的敬意!

然而疫情还是对测试工作产生了影响,因为学生不能返校,无法到在现场调试与测试。余子濠、蔡晔和刘彤三位挺身而出,协助调试测试工作。测试验证工作其实也是非常具有挑战性,因为从底层PCB版图、内存颗粒到中间处理器设计、到上层操作系统、应用软件,每个层次都可能出问题。哪怕一个小问题,都会造成芯片无法正常工作。

经过大约1个月的调试测试,终于证明芯片一切正常,可以启动Linux操作系统。但也发现了芯片的I/O模块存在bug,影响了SD卡的读写。测试验证也是充满了戏剧性。一开始调试时比较保守,将芯片降到了50MHz,没想到系统出现了很多问题。后来把芯片频率从50MHz跳到了200MHz,结果原来很多问题都消失了,能稳定地运行Linux。又进一步把频率提高到了350MHz,启动Linux出现了问题,但是可以稳定地运行RT-Thread。这个频率和后端仿真基本一致。这也验证了用Chisel开发和Verilog开发对后端物理设计并没有很大的影响。

五、毕业答辩演示

2020年6月2日,国科大本科生毕业设计答辩日。五位同学分别介绍了他们基于COOSCA处理器核的进一步优化工作:

王华强:《基于RISC-V的乱序多发射处理器设计》

张紫飞:《基于RISC-V的向量处理单元设计》

张林隽:《开源处理器分支预测器的设计与性能优化》

金越:《基于敏捷开发语言的开源处理器非阻塞缓存的设计与实现》

王凯帆:《RISC-V平台下的二进制翻译与优化》

其中王凯帆的毕业设计中使用了COOSCA核,也是他们自己设计的核首次在科研中得到应用。

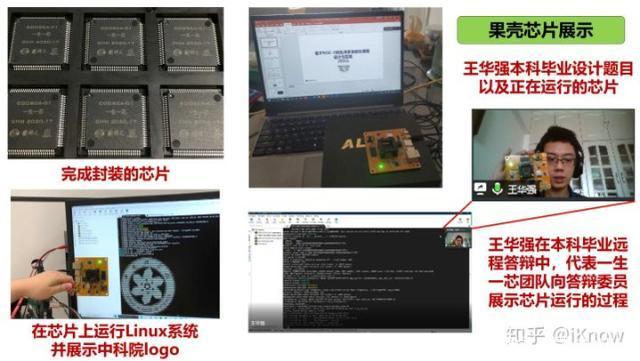

王华强同学代表「一生一芯」团队展示了COOSCA芯片的功能。他进一步又将这个核改进为乱序多发射,在FPGA上进行了测试验证,结果显示比COOSCA核的IPC提升了一倍。他的毕业设计也获得了国科大校级优秀毕业设计。

五位本科生,实现了带着自己设计的处理器芯片毕业这个目标!

后来,王凯帆又将国科大操作系统课程上同学们自己编写的UCAS-Core移植到了COOSCA核上,实现了用自己写的CPU运行自己写的操作系统这个小目标。

六、「果壳」公开亮相

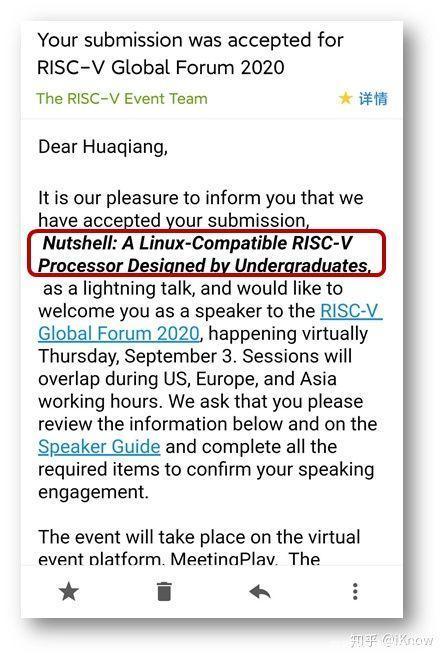

CRVA联盟将于7月18日召开RISC-V年中技术研讨会,「一生一芯」团队决定让王华强提交一份设计报告,正式向社区介绍COOSCA核的设计。提交前,大家觉得COOSCA是一个内部代号,现在要公开亮相了,应该有个正式一点的名字。同学们讨论后,决定改名为「果壳(NutShell)」,和国科大的「国科」同音。可以看得出来,他们对国科大确实有些深厚的情感。

五位同学开始一起为「果壳」的首次亮相做了大量准备工作:王凯帆整理了代码以及相应的文档,并在Github上开源,王华强整理了一份介绍「果壳」设计的报告PPT。7月18日,王华强在技术研讨会第二个出场,介绍了果壳的设计细节和一些开发过程中的经验体会。这是报告视频:

「果壳」设计开源链接:

7月22日,王华强又收到了「果壳」被RISC-VGlobalForum被接收的通知。9月3日,王华强同学将代表团队向全球业界介绍「果壳」的设计,这也是「果壳」首次在国际舞台上亮相。看了一下这次RISC-V全球论坛的日程,报告均来自世界各地的业界资深专家,还包括图灵奖得主DavidPatterson教授。国科大本科生能登上RISC-V全球论坛介绍他们设计的处理器核,这在国际上也是非常难得了。作为教学团队成员,我们内心也有一份自豪。

日程:

七、收获与体会

我们在调研中发现和「一生一芯」计划目标最接近的是2017年春季开始UCBerkeley开了一门新课EE194/290C「28nmSoCforIoT」,目标是设计一个SoC芯片,集成各种IP模块,包括一个Berkeley开发的RISC-VRocket处理器核。这门课以流片为目标,2017年春由9位本科生与1位研究生参加,通过1学期完成了流片,但未提供信息证明芯片能正常工作。

伯克利EE194/290C这门课是根据已有的RISC-V核和其他IP核进行SoC集成。而「一生一芯」与EE194/290C课程的区别在于要让本科生直接设计一款64位RISC-V处理器,然后在这个核的基础上,学生们需进一步集成与验证一系列外围IP,最终形成一个能运行Linux操作系统的SoC芯片,这极具挑战。

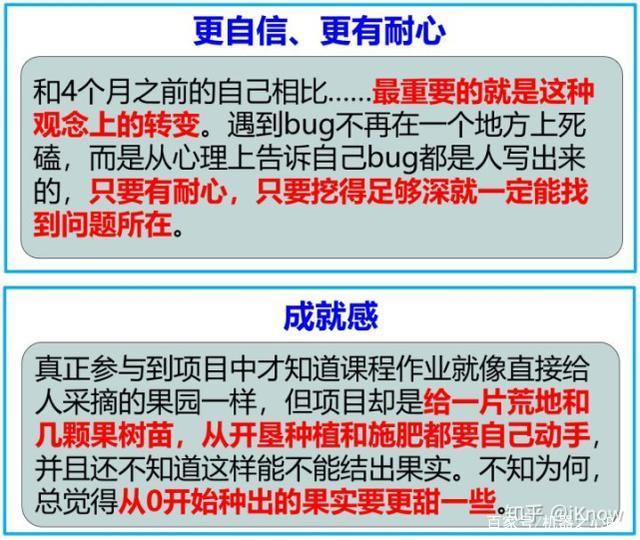

一年前,我们不知道这个目标是不是可行,最终能不能成功。但如今,我们探了回路,并且把路走通了,证明是可行的。这个摸索的过程积累了不少经验,也充满了教训。五位同学作为小白鼠参与首期「一生一芯」计划,成长了很多。他们不仅在项目中掌握了处理器芯片设计所需的专业知识,也锻炼出了优秀人才所具备的出色心理素质。一起来看看他们的感悟:

如今,这五位同学正在参与一个更有挑战的项目,开发一款高性能乱序多发射RISC-V处理器核的设计。一年前,他们在做「果壳」时还有些吃力,现在已是这个新团队中的骨干,和其他博士生和工程师们一起攻坚克难。去掉团队中蔡晔、唐丹和我这三位40岁以上的中年人,这支队伍平均年龄只有23.1岁,但他们表现出来的战斗力却是惊人的——不到三个星期就从头开始完成了乱序处理器主流水线的设计与实现,并且通过CoreMark测试。等到他们30岁时,就可以说已经是处理器芯片和计算机系统设计领域的「老兵」了。那时,他们将进入各自的工作岗位,也许去工业界研发产品,也许在学术界做科研。相信那时他们的创造力会得到更大的发挥和展现。我对这批年轻人的未来充满期待。

从教学团队角度来看,除了前期在总体方案、环境平台等方面需做好充分准备以外,在开发过程中有四方面指导尤其重要(以下为余子濠老师总结):

1.项目规划和分工。学生在开发初期不一定能完全掌握芯片中各个模块之前的关系,此时需要教师对学生的工作进行较为细致的分工,让学生通过一些初期的任务来认识芯片的全貌。随着项目的进行,学生对芯片的认识逐渐清晰之后,教师进行的分工可以向粗略的方向转变,向学生提出清晰的任务目标,并让学生尝试提出自己的解决方案。

2.引导学生了解项目中的每一处细节。芯片是一个复杂的系统,学生需对芯片每一个模块的行为都有所了解,还需要了解程序在芯片上运行的每一处细节。但是学生一开始往往不能从课程设计的模式中转变过来,认为只需要了解自己任务相关的模块即可,不去主动了解其它模块,不去了解软件层次的行为。这导致他们在遇到问题会想不出解决的思路。此时教师需要对学生进行引导,让他们主动去认识芯片甚至是软件行为的每一处细节。在遇到困难的时候,这些认识就会成为解决问题的线索,顺着线索去追溯问题的过程又会进一步加深学生对这些认识的理解,从而形成良性循环。

3.指导学生使用在课堂学习的知识解决开发中遇到的实际问题。芯片开发过程中可能会遇到各种困难,一些表面上看像是硬件设计的问题,最终可能是软件配置错误造成的。解决这些困难需要学生站在全局的视角来分析问题,并与课堂上学习到的知识建立联系,从中寻找解决问题的可能性。教师需要引导学生根据观测到的现象进行思维的发散,主动思考可能与哪些学过的知识建立联系。如果学生面对一些比较困难的问题,也会需要教师进行点拨。

4.引导学生正确认识探索过程中的不确定性。在一款功能完整的芯片,有一些关键模块的原理是课堂上没有详细介绍的,学生要正确地实现这些模块,需要一个探索的过程。这意味着学生不能像课程作业那样按部就班地完成,而是会经历设计方案的调整,甚至是整个方案的推倒重来。这容易导致学生感到焦虑或沮丧,因此教师需要对学生的心态进行正确的引导,告诉他们不确定性是探索过程中的客观规律,然后引导学生去总结探索失败的经验,去深刻地分析当前方案不可行的原因,从而加深对问题的理解,让学生正确认识到探索失败的意义。

举报/反馈